Назначение и область применения: Что такое UART и зачем он нужен?

Универсальный асинхронный приёмопередатчик (UART) — это один из наиболее фундаментальных и распространенных протоколов последовательной передачи данных в цифровой электронике. По своей сути, UART — это не просто стандарт связи, но и физический компонент (микросхема или блок внутри процессора), который преобразует параллельные данные из компьютерной шины в последовательный поток битов для передачи по одной линии, и выполняет обратное преобразование при приеме.

Для понимания протокола UART его можно представить как телеграфную линию. Вместо того чтобы передавать все 8 бит одного байта одновременно по 8 параллельным проводам, UART отправляет их друг за другом, бит за битом, по одному проводу.

Расшифровка названия

- Universal (Универсальный): Параметры передачи данных, такие как скорость, формат кадра и контроль четности, являются гибко настраиваемыми, что позволяет соединять широкий спектр устройств.

- Asynchronous (Асинхронный): Это ключевая особенность. В отличие от синхронных интерфейсов (таких как SPI или I2C), UART не требует отдельной линии для тактового сигнала, который бы синхронизировал отправителя и получателя. Вместо этого оба устройства заранее "договариваются" о скорости передачи. Синхронизация каждого пакета данных происходит с помощью специальных стартовых и стоповых битов.

- Receiver-Transmitter (Приёмопередатчик): Устройство UART способно как отправлять (Transmit, TX), так и принимать (Receive, RX) данные, обычно по двум выделенным для этого линиям.

Основное назначение

Главная задача UART — обеспечить простую и надежную двустороннюю (full-duplex) связь "точка-точка" между двумя цифровыми устройствами. Он является стандартом де-факто для всех для микроконтроллеров, периферийных модулей и компьютеров, позволяя им обмениваться информацией.

Область применения

Несмотря на свою простоту и возраст, UART остается чрезвычайно востребованным благодаря своей надежности и минимальным требованиям к аппаратной части. Его можно встретить в самых разных областях:

- Системная консоль и отладка: На Repka Pi и многих других одноплатных компьютерах один из UART-портов используется как отладочная консоль. Подключившись к нему, можно получить доступ к сообщениям загрузчика и операционной системы, даже если видеовыход не работает.

- Взаимодействие с периферийными модулями: Это основная сфера применения в DIY-проектах. Множество модулей используют UART для обмена данными:

- GPS-приемники (передают NMEA-сообщения с координатами).

- Bluetooth-модули (HC-05, HC-06).

- GSM/GPRS-модули (для отправки SMS и выхода в интернет).

- Считыватели RFID-карт.

- Программирование микроконтроллеров: Многие микроконтроллеры (например, Arduino, ESP8266/ESP32) прошиваются через UART.

- Промышленная автоматика: Различные датчики и исполнительные устройства в промышленном оборудовании часто используют UART поверх более надежных физических интерфейсов, таких как RS-232 или RS-485.

Ключевые понятия: Сигналы TX (Transmitter), RX (Receiver) и GND (Земля)

Для установления базового UART-соединения необходимы как минимум три электрических подключения. Каждое из них выполняет строго определенную функцию.

-

TX (Transmitter / Передатчик): Это линия, по которой устройство отправляет данные. С точки зрения устройства, пин TX является выходом (Output). Поток битов направлен от TX-пина во внешний мир.

-

RX (Receiver / Приёмник): Это линия, по которой устройство принимает данные. С точки зрения устройства, пин RX является входом (Input). Поток битов направлен из внешнего мира в RX-пин.

-

GND (Ground / Земля): Это общая точка отсчета напряжения для обоих устройств. Без общего провода земли логический

HIGH(+3.3V) одного устройства не будет корректно распознан другим, так как у них не будет единого "нулевого уровня". Наличие общего провода земли является обязательным условием для любой цифровой связи.

Фундаментальное правило подключения: Перекрестное соединение

Самый важный принцип при физическом соединении двух устройств по UART — это перекрестное подключение линий TX и RX. Поскольку линия TX является выходом для исходящего потока данных, а линия RX — входом для входящего, для установления двусторонней связи необходимо соединить выход одного устройства со входом другого.

TXустройства А ->RXустройства БRXустройства А <-TXустройства БGNDустройства А <->GNDустройства Б

Ошибка в этом подключении (например, соединение TX с TX) является наиболее частой причиной, почему UART-связь не устанавливается.

Принцип асинхронной связи: Как устройства общаются без общего тактового сигнала

Ключевая особенность UART — отсутствие отдельной линии для тактового сигнала (Clock), которая бы диктовала принимающей стороне, в какой именно момент времени нужно считывать бит с линии данных. Вместо этого асинхронная связь опирается на два фундаментальных принципа:

-

Предварительная договоренность о скорости (Baud Rate): Перед началом обмена данными оба устройства должны быть сконфигурированы на работу с абсолютно одинаковой скоростью передачи, измеряемой в битах в секунду (бод). Этот параметр определяет длительность каждого бита, позволяя принимающему устройству считывать (сэмплировать) состояние линии в правильные моменты времени.

-

Синхронизация по каждому байту: Даже при одинаковой скорости, внутренние часы устройств могут незначительно расходиться. Чтобы решить эту проблему, каждый передаваемый байт "заворачивается" в специальную оболочку — кадр (frame), который позволяет получателю синхронизироваться в начале каждого байта.

- Состояние покоя (Idle): Когда данные не передаются, линия TX удерживается в состоянии

HIGH. - Стартовый бит (Start Bit): Передача начинается с того, что отправитель переводит линию в состояние

LOWна один бит-период. Этот переход сHIGHнаLOWявляется сигналом "Внимание!" для приемника. Увидев его, приемник запускает свой внутренний таймер. - Биты данных: Опираясь на заранее известную скорость, приемник начинает считывать состояние линии через равные промежутки времени, точно в середине каждого бит-периода, чтобы получить 5-8 бит полезных данных.

- Стоповый бит (Stop Bit): В конце передачи отправитель возвращает линию в состояние

HIGHкак минимум на один бит-период. Это гарантирует, что следующий стартовый бит будет корректно распознан.

- Состояние покоя (Idle): Когда данные не передаются, линия TX удерживается в состоянии

Таким образом, вместо постоянной синхронизации по общему тактовому сигналу, UART выполняет быструю микро-синхронизацию в начале каждого передаваемого байта.

Сравнение с другими интерфейсами (I2C, SPI)

Чтобы лучше понять место UART в иерархии протоколов, полезно сравнить его с двумя другими популярными последовательными интерфейсами, также доступными на Repka Pi.

| Параметр | UART | I2C (Inter-Integrated Circuit) | SPI (Serial Peripheral Interface) |

|---|---|---|---|

| Количество проводов | 2 (TX, RX) + GND | 2 (SDA, SCL) + GND | 4+ (MOSI, MISO, SCLK, CS) + GND |

| Тип связи | "Точка-точка" (один к одному). | "Общая шина" (много ведущих, много ведомых). | "Ведущий-ведомый" (один ведущий, много ведомых). |

| Синхронизация | Асинхронная (без тактового сигнала). | Синхронная (линия SCL). | Синхронная (линия SCLK). |

| Скорость | Относительно низкая (до ~1 Мбит/с). | Средняя (100 кбит/с - 3.4 Мбит/с). | Очень высокая (до 100+ Мбит/с). |

| Основное применение | Связь с ПК, GPS, Bluetooth, отладочные консоли. | Связь с медленными датчиками (температуры, давления), EEPROM. | Связь с быстрыми устройствами (экраны, SD-карты, АЦП). |

Вывод: UART является идеальным выбором для простой и надежной связи между двумя устройствами, особенно на больших расстояниях (при использовании преобразователей уровней, таких как RS-232), когда не требуется высокая скорость или подключение множества устройств к одной шине.

Конечно. Я подготовлю максимально подробное и исчерпывающее описание принципов передачи данных по UART, как вы и просили. Каждый аспект будет разобран в деталях, чтобы не осталось никаких неясностей.

Принципы передачи данных

Асинхронная передача данных по протоколу UART — это строго регламентированный процесс. Информация не передается сплошным потоком; вместо этого она разбивается на небольшие, стандартизированные пакеты, называемые кадрами (frames). Понимание структуры этого кадра и параметров, управляющих его передачей, является ключом к успешной настройке UART-соединения.

Структура UART-кадра (фрейма)

Каждый кадр представляет собой последовательность битов, которая обычно переносит один байт (8 бит) полезной информации. Он имеет четкую структуру, позволяющую принимающему устройству синхронизироваться и корректно интерпретировать данные без наличия общего тактового сигнала.

Визуально последовательность передачи одного кадра на линии TX выглядит следующим образом:

Рассмотрим каждый компонент этого кадра в деталях.

Стартовый бит (Start Bit)

- Назначение: Синхронизация и оповещение о начале передачи.

- Механизм: Когда линия передачи находится в состоянии покоя (Idle), она удерживается на высоком логическом уровне (

HIGH). Для инициации передачи данных передатчик (TX) принудительно переводит линию в низкий логический уровень (LOW) ровно на один бит-период. Этот резкий переход сHIGHнаLOWявляется сигналом для приемника (RX). Обнаружив этот спадающий фронт, приемник "пробуждается", запускает свой внутренний таймер и готовится к приему последующих битов данных с заранее оговоренной скоростью. Стартовый бит всегда один, и он всегда имеет значениеLOW.

Биты данных (Data Bits)

- Назначение: Передача полезной информации.

- Механизм: Сразу после стартового бита следуют биты данных. Их может быть от 5 до 8, но в подавляющем большинстве современных приложений используется 8 бит для передачи одного байта.

- Ключевая особенность: Данные передаются, начиная с младшего бита (Least Significant Bit, LSB). Это означает, что если мы передаем байт

0b11001010, то последовательность на линии будет0, 1, 0, 1, 0, 0, 1, 1. Приемник, зная это правило, собирает биты в правильном порядке.

Бит чётности (Parity Bit) - опционально

- Назначение: Простейшая форма проверки целостности данных.

- Механизм: Это необязательный бит, который добавляется после битов данных. Его значение вычисляется таким образом, чтобы общее количество единиц (логический

HIGH) в битах данных (и иногда включая сам бит четности) было либо чётным (Even Parity), либо нечётным (Odd Parity).- Even Parity (Проверка на чётность): Если в битах данных уже содержится чётное число единиц, бит четности будет

0. Если нечётное —1. - Odd Parity (Проверка на нечётность): Если в битах данных нечётное число единиц, бит четности будет

0. Если чётное —1.

- Even Parity (Проверка на чётность): Если в битах данных уже содержится чётное число единиц, бит четности будет

- Приемник выполняет тот же подсчет и сравнивает результат. Если он не совпадает, значит, в процессе передачи произошла ошибка (например, из-за помех). В большинстве современных систем, где проверка ошибок реализована на более высоких уровнях протокола, бит четности отключают (

No Parity).

Стоповый бит (Stop Bit)

- Назначение: Обозначение конца кадра и гарантия корректного начала следующей передачи.

- Механизм: После передачи последнего бита данных (или бита четности) передатчик переводит линию обратно в высокий логический уровень (

HIGH) на определенный период времени. Длительность этого периода может составлять 1, 1.5 или 2 бит-периода. Наиболее распространенным является один стоповый бит. - Стоповый бит критически важен, так как он гарантирует, что линия вернется в состояние

HIGHперед началом следующей передачи. Это обеспечивает четкий и однозначный спадающий фронт для следующего стартового бита, даже если последний бит данных былLOW.

Конфигурация формата кадра часто записывается в виде 8N1, что означает: 8 битов данных, No Parity (без бита четности), 1 стоповый бит. Это самая распространенная конфигурация на сегодняшний день.

Скорость передачи данных (Baud Rate)

- Определение: Скорость передачи данных (Baud Rate, или бод) — это фундаментальный параметр UART, определяющий, сколько раз в секунду изменяется состояние сигнала на линии передачи. В контексте UART это эквивалентно количеству бит в секунду.

- Принцип согласования: Так как протокол является асинхронным, оба устройства — передатчик и приемник — должны быть заранее настроены на абсолютно одинаковую скорость. Если скорости не совпадают, приемник будет считывать состояние линии в неправильные моменты времени, что приведет к полной потере и искажению данных (на выходе будут нечитаемые символы, "кракозябры").

- Связь с длительностью бита: Скорость напрямую определяет длительность одного бита.

Длительность_бита (в секундах) = 1 / Baud_Rate. Например, при скорости 9600 бод каждый бит занимает1/9600 ≈ 104.17микросекунды. - Стандартные значения: Существует ряд стандартных скоростей, поддерживаемых большинством устройств: 1200, 2400, 4800, 9600 (часто используется по умолчанию), 19200, 38400, 57600, 115200 (распространенная скорость для прошивки и быстрой передачи данных) и выше.

Контроль потока (Flow Control) - краткий обзор

- Назначение: Контроль потока — это механизм, который предотвращает потерю данных в ситуации, когда передатчик отправляет информацию быстрее, чем приемник успевает ее обрабатывать. Когда буфер приемника близок к заполнению, он может послать передатчию сигнал "подожди", и наоборот, сигнал "продолжай", когда буфер освободится.

- Типы контроля потока:

- Программный (Software Flow Control): Использует специальные управляющие символы (

XONдля возобновления,XOFFдля приостановки), которые передаются по тем же линиям TX/RX, что и основные данные. Этот метод не требует дополнительных проводов, но может давать сбои, если эти управляющие символы встречаются в самом потоке данных. - Аппаратный (Hardware Flow Control): Использует две дополнительные физические линии: RTS (Request to Send) и CTS (Clear to Send). Это гораздо более надежный метод, так как управляющие сигналы передаются отдельно от данных.

- Программный (Software Flow Control): Использует специальные управляющие символы (

Аппаратная реализация UART на Repka Pi

Для эффективного использования UART-интерфейса необходимо понимать, что он представляет собой не просто программную абстракцию, а полноценный аппаратный компонент, интегрированный в однокристальную систему (SoC). Эта глава посвящена рассмотрению архитектуры и принципов работы UART на аппаратном уровне.

UART как аппаратный блок в однокристальной системе Allwinner H6

В современных процессорах, таких как Allwinner H6, используемом в Repka Pi 4, периферийные устройства являются независимыми аппаратными блоками (также известными как IP-блоки). UART-контроллер — это не эмуляция, а специализированная микросхема, физически реализованная на том же кристалле, что и центральный процессор.

Такой подход имеет фундаментальное преимущество: он разгружает центральный процессор (ЦП). Вместо того чтобы ЦП тратил свои такты на ручное формирование последовательного потока битов (процесс, известный как "bit-banging"), он делегирует эту задачу специализированному UART-контроллеру. Этот контроллер самостоятельно управляет стартовыми/стоповыми битами, скоростью передачи и форматом кадра, позволяя основным ядрам процессора заниматься выполнением высокоуровневых задач.

Связь с другими системными блоками: System Peripheral (GIC, DMA) и ARM Cortex-A53

Эффективная работа UART-контроллера невозможна в изоляции. Он тесно интегрирован с другими критически важными компонентами системы:

-

ARM Cortex-A53(Центральный процессор): ЦП выступает в роли "командного центра". Он выполняет код драйвера операционной системы, который:- Конфигурирует UART-контроллер: записывает в его регистры значения скорости (Baud Rate), формата кадра (например, 8N1) и другие параметры.

- Обрабатывает результаты: читает данные, принятые UART, или записывает данные для передачи.

-

System Peripheral(Системная периферия): Этот блок является "нервной системой" SoC и содержит два ключевых для работы UART компонента:GIC(Generic Interrupt Controller / Общий контроллер прерываний): Когда UART-контроллер завершает операцию (например, принял байт данных или его буфер для передачи освободился), он посылает электрический сигнал — прерывание — в GIC. Контроллер GIC немедленно уведомляет об этом ЦП. Это позволяет системе работать в событийно-ориентированном режиме: процессор не тратит время на постоянный опрос UART, а "просыпается" только тогда, когда действительно есть работа.DMA(Direct Memory Access / Прямой доступ к памяти): Это специализированный сопроцессор для пересылки данных. Для высокоскоростных потоков ЦП может дать команду DMA-контроллеру: "скопируй 10 килобайт данных из оперативной памяти напрямую в передающий буфер UART". DMA выполнит эту операцию в фоновом режиме, полностью освободив ЦП. Это является ключом к достижению максимальной пропускной способности без существенной нагрузки на систему.

Таким образом, UART — это не просто порт, а часть сложной экосистемы, где ЦП задает стратегию, а GIC и DMA обеспечивают эффективное и высокопроизводительное тактическое исполнение.

Доступные UART-контроллеры

Аппаратный потенциал однокристальной системы определяет, сколько независимых последовательных портов может быть доступно пользователю. Характеристики SoC Allwinner H6 задают основу для этих возможностей.

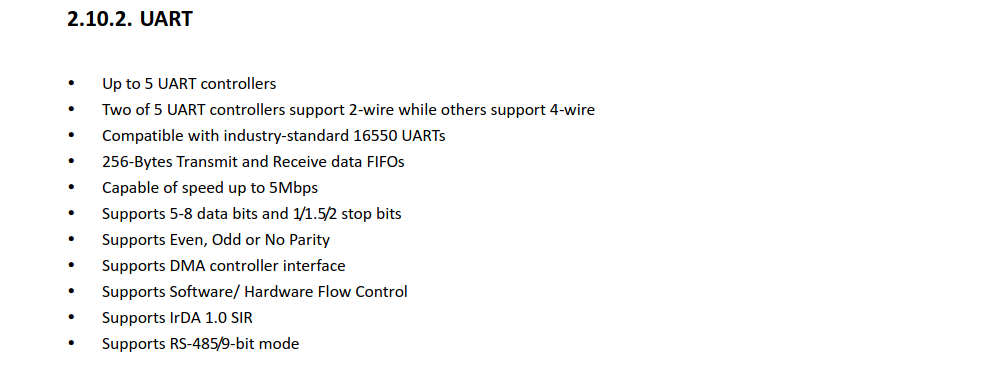

Анализ даташита: "Up to 5 UART controllers". Что это означает на практике?

Анализ даташита: "Up to 5 UART controllers". Что это означает на практике?

Спецификация "до 5 UART-контроллеров" является ключевой. Она означает, что внутри кристалла Allwinner H6 физически существует пять независимых, полноценных аппаратных блоков UART. Каждый из этих блоков способен вести собственную, параллельную сессию асинхронной связи.

Однако фраза "до" (up to) имеет важное практическое значение. Она указывает на гибкость системы мультиплексирования портов, известной как Pin Control (Pinctrl). Физические выводы (ножки) процессора являются многофункциональными. Один и тот же пин может быть сконфигурирован программно как:

- Обычный GPIO-пин.

- Линия

TXдляUART2. - Линия

SDAдляI2C1. - Или выполнять другую альтернативную функцию.

Таким образом, хотя SoC предоставляет 5 аппаратных контроллеров, количество UART-портов, реально доступных пользователю на 40-контактной гребенке Repka Pi, определяется двумя факторами:

- Схемотехникой платы: Какие именно линии от UART-контроллеров инженеры физически развели на гребенку GPIO.

- Конфигурацией дерева устройств (Device Tree): Какой режим по умолчанию назначен для этих многофункциональных пинов в операционной системе Linux.

На практике это означает, что пользователь имеет доступ к нескольким (но не обязательно ко всем пяти) UART-портам, которые не задействованы для других критически важных функций.

Разделение ролей: UART0 и пользовательские порты

Из доступных контроллеров один традиционно имеет особый статус, в то время как остальные предоставляются для свободного использования.

-

UART0: Системная отладочная консоль Первый UART-контроллер (UART0) практически всегда зарезервирован ядром операционной системы под последовательную консоль. Это самый низкоуровневый текстовый интерфейс для взаимодействия с устройством. Через него выводятся:- Сообщения начального загрузчика (U-Boot).

- Диагностические сообщения ядра Linux в процессе загрузки.

- Интерфейс командной строки (shell) после полной загрузки системы.

Использование

UART0для подключения периферии категорически не рекомендуется, так как поток данных от вашего устройства будет смешиваться с системными сообщениями, что приведет к непредсказуемому поведению и потере данных. -

Пользовательские UART-порты (

UART1,UART2и т.д.) Остальные UART-контроллеры, выведенные на гребенку, являются "чистыми" и предназначены для подключения пользовательских устройств: GPS-модулей, Bluetooth-адаптеров, GSM-модемов, других микроконтроллеров и любых устройств, использующих последовательный интерфейс.

Совместимость со стандартом 16550: Почему это важно для драйверов Linux

В списке характеристик указано: "Compatible with industry-standard 16550 UARTs". Это одно из важнейших преимуществ UART-контроллеров Allwinner.

-

Исторический стандарт:

16550 UART— это название серии микросхем, которые стали промышленным стандартом для последовательных портов (COM-портов) в персональных компьютерах на протяжении десятилетий. Их архитектура, набор регистров и принципы управления хорошо известны и изучены. -

Принцип совместимости: Инженеры Allwinner не стали изобретать полностью новый, проприетарный интерфейс для своих UART-контроллеров. Вместо этого они спроектировали их таким образом, чтобы они были регистрово-совместимы (register-compatible) со стандартом 16550. Это означает, что их внутренние управляющие регистры (для данных, статуса, управления) имеют те же смещения и выполняют те же функции, что и в классической микросхеме 16550.

-

Преимущество для Linux: Эта совместимость позволяет ядру Linux использовать свой универсальный, отлаженный и высокооптимизированный драйвер последовательных портов (8250/16550 serial driver) для управления UART на Repka Pi. Вместо необходимости писать и поддерживать специфичный драйвер для Allwinner, система использует стандартный, проверенный временем код. Для конечного пользователя это означает высокую стабильность, предсказуемость работы и автоматическое появление знакомых файлов устройств

/dev/ttyS*без дополнительных усилий.

Конечно. Мы разберем, как абстрактные функции, заложенные в кристалле процессора, находят свой путь к физическим контактам на гребенке GPIO, и где именно их искать.

Физический уровень: От кристалла до гребенки GPIO

После рассмотрения архитектуры SoC и доступных UART-контроллеров, необходимо понять, как именно эти внутренние логические блоки соединяются с внешним миром. Этот процесс управляется на самом низком уровне и определяет, какие физические пины на 40-контактной гребенке будут выполнять функции TX и RX.

Механизм Pin Control (Pinctrl): Как один и тот же физический пин может быть и GPIO, и линией UART_TX

Физические выводы (ножки) процессора Allwinner являются многофункциональными. Это означает, что один и тот же контакт может выполнять совершенно разные роли в зависимости от конфигурации. За переключение этих ролей отвечает специальный аппаратный блок — мультиплексор (MUX).

Представьте мультиплексор как сложный электронный переключатель, который стоит между физическим пином и несколькими внутренними блоками SoC (контроллером GPIO, контроллером UART, контроллером SPI и т.д.). Этот переключатель может соединить пин только с одним из этих блоков в каждый момент времени.

Управление этим мультиплексором осуществляется подсистемой ядра Linux под названием Pin Control (Pinctrl). Конфигурация для этой подсистемы загружается на самом раннем этапе старта системы из специального файла — Дерева устройств (Device Tree). Именно в этом файле-конфигурации для каждой конкретной модели платы (например, Repka Pi 4) прописано, какой пин какую функцию должен выполнять по умолчанию.

Таким образом, когда вы используете пин для UART:

- Ядро Linux при загрузке читает Дерево устройств.

- Подсистема

Pinctrlнастраивает мультиплексор для нужного пина. - Мультиплексор физически отключает пин от общего контроллера GPIO и подключает его напрямую к выходу

TX(или входуRX) соответствующего UART-контроллера.

С этого момента данный пин перестает быть "контактом общего назначения" и становится специализированной линией последовательного порта, полностью управляемой UART-драйвером ядра.

Распиновка (Pinout): Нахождение физических контактов TX и RX для доступных UART-портов

Расположение UART-пинов на 40-контактной гребенке является фиксированным для каждой модели платы. Крайне важно сверяться со схемой распиновки (pinout) именно для вашей версии Repka Pi, чтобы избежать ошибок подключения.

Важное примечание: Помимо

TXиRX, для стабильной работы UART всегда необходимо соединять общую землю (GND) между устройствами. На гребенке Repka Pi доступно несколько пиновGND.

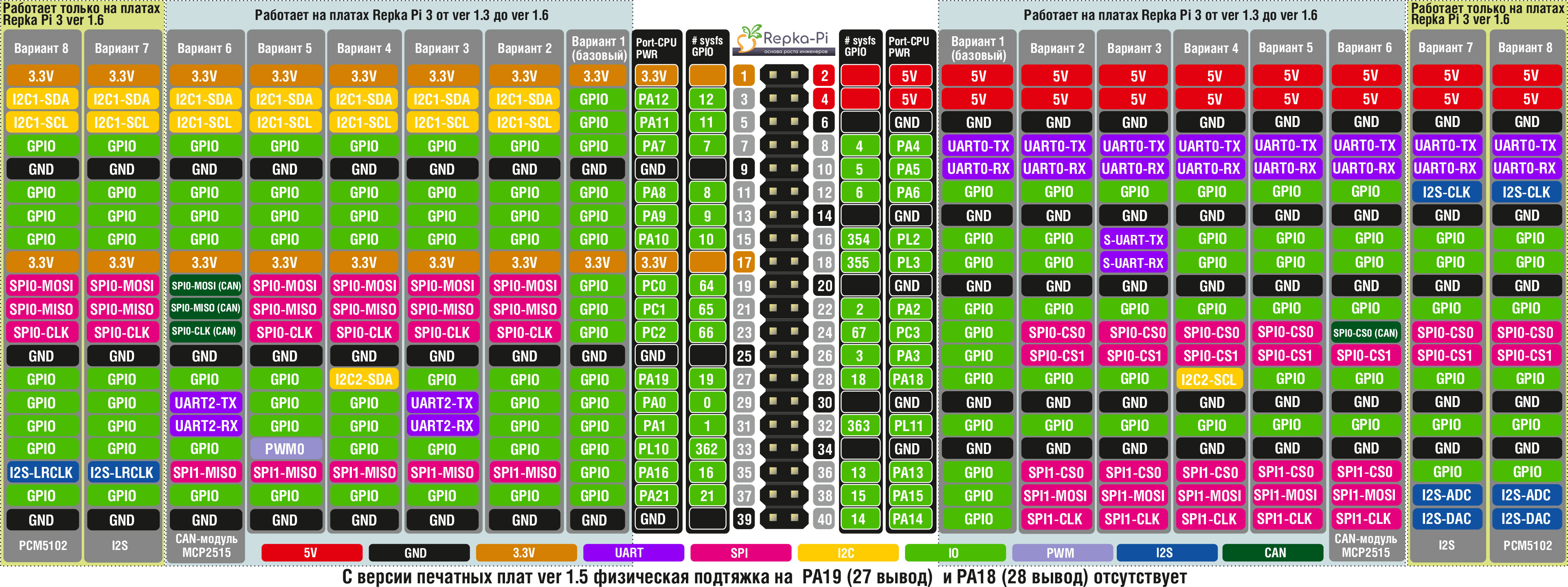

Расположение пинов для Repka Pi 3

На Repka Pi 3 для пользовательских проектов наиболее доступен UART0.

UART0_TX: Пин 8 (BOARD)UART0_RX: Пин 10 (BOARD)GND: Пин 6, 9, 14, 20, 25, 30, 34, 39 (BOARD)

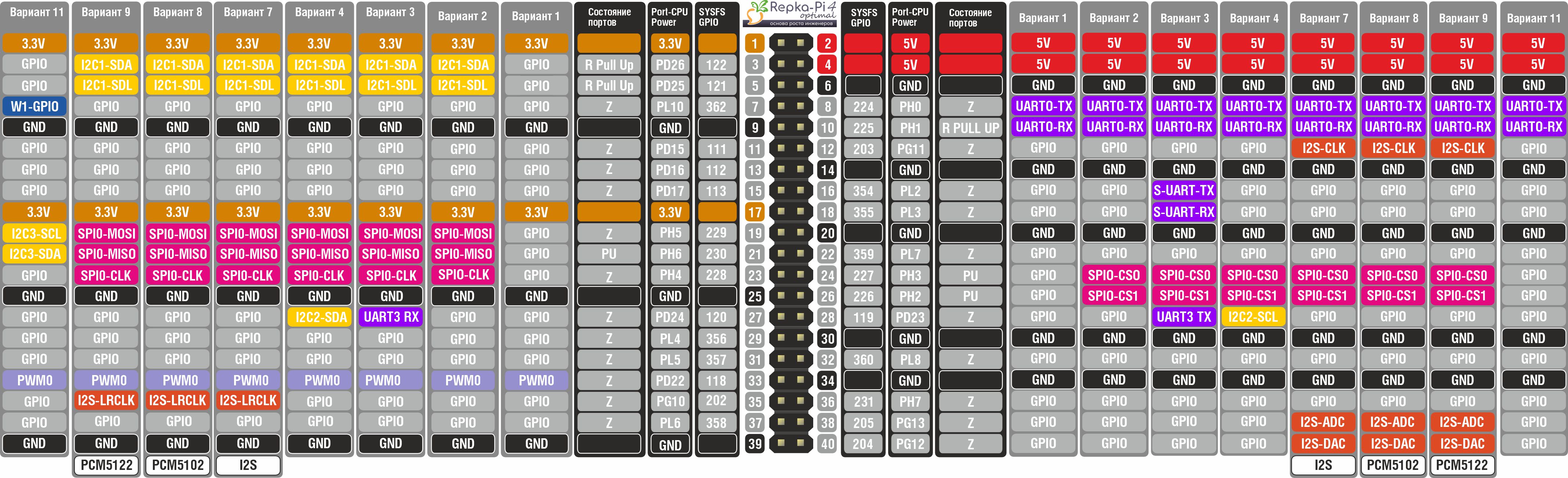

Расположение пинов для Repka Pi 4

На Repka Pi 4 основной пользовательский порт UART0 выведен на те же физические пины, что и у Repka Pi 3, для сохранения совместимости.

UART0_TX: Пин 8 (BOARD)UART0_RX: Пин 10 (BOARD)GND: Пин 6, 9, 14, 20, 25, 30, 34, 39 (BOARD)

Аппаратное ускорение: Ключ к высокой производительности

Современные приложения часто требуют обмена большими объемами данных по последовательному порту, например, при получении потока координат от GPS или при работе с GSM-модемом. Для эффективной работы в таких условиях SoC Allwinner H6 оснащен мощными механизмами аппаратного ускорения, которые минимизируют нагрузку на центральный процессор.

Проблема: Почему простая побайтовая передача неэффективна для процессора

Рассмотрим наивный подход к работе с UART. В такой модели процессор должен был бы участвовать в передаче и приеме каждого отдельного байта.

- При приеме: На каждый принятый байт UART-контроллер генерирует прерывание. Процессор вынужден:

- Немедленно остановить свою текущую задачу.

- Сохранить свой текущий контекст (состояние регистров).

- Перейти к выполнению кода обработчика прерывания.

- Считать один байт из регистра данных UART.

- Поместить этот байт в буфер в оперативной памяти.

- Восстановить свой контекст и вернуться к прерванной задаче.

- При передаче: Процесс аналогичен, но в обратную сторону.

Этот процесс, называемый прерыванием на каждый символ (per-character interrupt), имеет колоссальные накладные расходы. На скорости 115200 бод (около 11 520 байт/с) процессор будет прерываться более 11 тысяч раз в секунду. На более высоких скоростях, таких как 1 Мбит/с, накладные расходы на обработку прерываний могут полностью парализовать процессор, не оставляя ему времени на выполнение каких-либо других полезных задач.

Решение №1: Буферы FIFO (First-In, First-Out)

Первый и самый важный уровень аппаратного ускорения — это наличие встроенных буферов.

-

Анализ даташита: В спецификации указано: "

256-Bytes Transmit and Receive data FIFOs". -

Принцип работы: UART-контроллер в Allwinner H6 оснащен двумя независимыми аппаратными "очередями" (буферами) по 256 байт каждая:

- Transmit FIFO (TX FIFO): Когда программе нужно отправить данные, драйвер ядра не отправляет их по одному байту. Вместо этого он может "выгрузить" в TX FIFO сразу целый блок данных (до 256 байт) одной быстрой операцией. После этого UART-контроллер самостоятельно и аппаратно извлекает байты из этой очереди один за другим и отправляет их в последовательную линию в соответствии с заданной скоростью.

- Receive FIFO (RX FIFO): Принимаемые извне байты не сразу вызывают прерывание, а сначала накапливаются в RX FIFO. Прерывание генерируется только тогда, когда количество данных в буфере достигает определенного порога (например, заполнен на 50% или 75%).

-

Эффект: Использование FIFO кардинально снижает количество прерываний. Вместо прерывания на каждый байт, процессор получает одно прерывание на целый блок данных (например, на каждые 128 принятых байт). Пока UART-контроллер аппаратно заполняет или опустошает свои буферы, центральный процессор свободен и может выполнять другие, более важные задачи. Это повышает общую производительность системы в десятки и сотни раз.

Решение №2: Прямой доступ к памяти (DMA)

Для максимальной производительности при работе с очень большими и непрерывными потоками данных используется второй, еще более мощный механизм ускорения.

-

Анализ даташита: В спецификации указано: "

Supports DMA controller interface". -

Принцип работы: UART-контроллер спроектирован так, что может напрямую взаимодействовать со специализированным сопроцессором — контроллером прямого доступа к памяти (DMA). Процесс передачи данных с использованием DMA выглядит следующим образом:

- Инициация: Центральный процессор (ЦП) один раз настраивает DMA-контроллер. Он дает ему команду: "Возьми блок данных размером 10 КБ, который начинается по этому адресу в оперативной памяти, и передай его в регистр данных UART-контроллера. Когда закончишь, сообщи мне".

- Пересылка данных: DMA-контроллер выполняет эту задачу полностью самостоятельно, без какого-либо участия ЦП. Он напрямую читает данные из оперативной памяти и записывает их в UART (чаще всего, в его TX FIFO).

- Завершение: Когда весь блок данных передан, DMA-контроллер генерирует одно-единственное прерывание, чтобы уведомить ЦП о завершении операции.

-

Эффект: Нагрузка на ЦП во время передачи данных стремится к нулю. Процессор освобождается от рутинной задачи пересылки байтов и может полностью посвятить себя обработке данных или выполнению пользовательского приложения.

Дополнительные аппаратные возможности

Помимо базовой передачи данных и механизмов ускорения, UART-контроллеры в SoC Allwinner H6 обладают рядом дополнительных аппаратных функций. Эти возможности обеспечивают повышенную надежность и совместимость при работе в сложных или нестандартных сценариях.

Аппаратный контроль потока (Hardware Flow Control)

При работе на высоких скоростях может возникнуть ситуация, когда принимающее устройство не успевает обрабатывать данные так же быстро, как их отправляет передатчик. Это может привести к переполнению аппаратного буфера RX FIFO и, как следствие, к потере данных. Для предотвращения таких ситуаций используется механизм контроля потока.

-

Анализ даташита: Спецификации содержат два ключевых пункта:

- "

Supports Software/Hardware Flow Control": Это подтверждает, что контроллер аппаратно поддерживает оба метода управления потоком. - "

Two of 5 UART controllers support 2-wire while others support 4-wire": Эта характеристика раскрывает важную деталь реализации.2-wire: Стандартное подключение (TX, RX), которое не поддерживает аппаратный контроль потока.4-wire: Расширенное подключение, которое добавляет две дополнительные сигнальные линии — RTS (Request to Send) и CTS (Clear to Send).

- "

-

Что это и как работает: Аппаратный контроль потока — это элегантный механизм "рукопожатия" между двумя устройствами.

- Когда буфер приемника (устройство А) почти заполнен, его UART-контроллер аппаратно изменяет состояние на своей линии RTS, подавая передатчику (устройству Б) сигнал "Прошу приостановить передачу".

- Передатчик (устройство Б) постоянно отслеживает состояние своей линии CTS, которая подключена к RTS устройства А. Увидев сигнал приостановки, он аппаратно прекращает отправку данных.

- Когда приемник (устройство А) освобождает свой буфер, он снова изменяет состояние линии RTS, сигнализируя "Готов к приему". Передатчик (устройство Б) видит это на своей линии CTS и возобновляет передачу.

Этот процесс происходит полностью на аппаратном уровне, без участия центрального процессора, что обеспечивает мгновенную реакцию и гарантирует отсутствие потерь данных. Наличие трех (из пяти) "полнофункциональных" 4-проводных UART-контроллеров делает Repka Pi пригодной для надежной работы с высокоскоростными периферийными устройствами, такими как сотовые модемы.

Гибкая настройка формата кадра

Протокол UART существует уже много десятилетий, и за это время появилось множество его вариаций для взаимодействия с различным оборудованием. UART-контроллер в Allwinner H6 спроектирован с учетом этой истории и обеспечивает максимальную совместимость.

-

Анализ даташита: Спецификации указывают на полную аппаратную поддержку различных форматов кадра:

- "

Supports 5-8 data bits and 1/1.5/2 stop bits" - "

Supports Even, Odd or No Parity"

- "

-

Что это и зачем нужно: Эти параметры позволяют UART-контроллеру на Repka Pi гибко настраивать последовательный протокол.

- Длина слова данных (5-8 бит): Хотя современным стандартом является 8 бит (один байт), некоторое унаследованное оборудование все еще может использовать 7-битные фреймы для передачи символов ASCII. Аппаратная поддержка этого режима обеспечивает обратную совместимость.

- Количество стоповых битов (1, 1.5, 2): В старых, медленных электромеханических устройствах (например, телетайпах) требовалось больше времени для обработки принятого символа. Использование 1.5 или 2 стоповых битов искусственно увеличивало паузу между кадрами, давая механизмам время подготовиться к приему следующего.

- Контроль четности (Even, Odd, No Parity): Как было описано ранее, это аппаратный механизм простейшей проверки ошибок.

Наличие всех этих опций на аппаратном уровне означает, что драйвер операционной системы может гибко сконфигурировать порт для взаимодействия с практически любым устройством, использующим асинхронный последовательный интерфейс, будь то современный GPS-модуль, работающий в режиме 8N1 (8 бит данных, без четности, 1 стоповый бит), или устаревшее промышленное оборудование, требующее режима 7E2 (7 бит данных, с контролем по четности, 2 стоповых бита).

Архитектура регистров UART

До сих пор мы рассматривали UART с точки зрения его логической работы и представления в операционной системе. Однако в основе всего этого лежит набор аппаратных регистров внутри SoC Allwinner, которыми управляет драйвер ядра. Понимание назначения этих регистров позволяет увидеть, как высокоуровневые команды (например, настройка скорости или отправка байта) транслируются в низкоуровневые операции с "железом".

Обзор ключевых регистров UART

UART-контроллер, совместимый со стандартом 16550, содержит несколько ключевых регистров. Хотя их физические адреса могут меняться, их функции остаются неизменными.

RBR (Receive Buffer Register) и THR (Transmit Holding Register)

- Назначение: Это "почтовые ящики" для данных.

- Принцип работы: Эти два 8-битных регистра часто занимают один и тот же адрес в памяти. Операционная система определяет, с каким из них она работает, по типу операции:

- Запись (Write): Когда процессор (или DMA) записывает байт по этому адресу, он попадает в

THR(Регистр хранения передатчика). Отсюда UART-контроллер забирает его для последовательной отправки. - Чтение (Read): Когда процессор читает байт с этого адреса, он забирает его из

RBR(Регистр буфера приемника), куда UART-контроллер поместил последний полностью принятый и собранный из битов байт.

- Запись (Write): Когда процессор (или DMA) записывает байт по этому адресу, он попадает в

LSR (Line Status Register) - Регистр статуса линии

- Назначение: Это "информационная панель" или "приборный щиток" UART-контроллера. Он содержит набор однобитных флагов, которые отражают текущее состояние процесса приема/передачи.

- Ключевые флаги:

DR(Data Ready): Флаг "Данные готовы". Устанавливается в1, когда в регистреRBRпоявился новый, еще не прочитанный байт. Драйвер постоянно следит за этим флагом, чтобы знать, когда нужно забирать данные.THRE(Transmit Holding Register Empty): Флаг "Регистр хранения передатчика пуст". Устанавливается в1, когдаTHRсвободен и готов принять следующий байт для отправки.- Флаги ошибок:

OE(Overrun Error - ошибка переполнения, новый байт пришел до того, как был прочитан старый),PE(Parity Error - ошибка четности) и др.

LCR (Line Control Register) - Регистр управления линией

- Назначение: Это главный "пульт настроек", который определяет формат UART-кадра.

- Настраиваемые параметры:

- Длина слова (WLS - Word Length Select): Биты, устанавливающие количество битов данных (5, 6, 7 или 8).

- Количество стоповых битов (STB - Stop Bits): Бит, выбирающий 1 или 2 стоповых бита.

- Контроль четности (PEN - Parity Enable, EPS - Even Parity Select): Биты для включения/выключения бита четности и выбора его типа (чётный/нечётный).

- Особая роль -

DLAB(Divisor Latch Access Bit): Этот бит вLCRявляется "переключателем режимов". Когда он установлен в1, он временно изменяет назначение адресов регистровRBR/THRиIER, предоставляя доступ к регистрамDLLиDLHдля настройки скорости.

DLL / DLH (Divisor Latch LSB / MSB) - Регистры делителя скорости

- Назначение: Установка скорости передачи данных (Baud Rate).

- Принцип работы: Скорость не устанавливается напрямую. Вместо этого в эти регистры записывается 16-битное число-делитель. UART-контроллер получает на вход высокочастотный тактовый сигнал от системы (например, 100 МГц) и делит его на это число, чтобы получить нужную скорость на выходе.

Формула (упрощенно): Baud Rate = (Частота_входного_сигнала) / (16 * Делитель)

- Так как делитель — 16-битный, а регистры — 8-битные, он разделяется на две части:

DLL(Divisor Latch LSB): Младшие 8 бит делителя.DLH(Divisor Latch MSB): Старшие 8 бит делителя.

- Доступ к этим регистрам возможен только после установки бита

DLABв регистреLCR.

Почему мы не управляем регистрами UART напрямую: Роль драйвера ядра Linux

Хотя знание архитектуры регистров полезно, прямое управление ими из пользовательской программы (например, через /dev/mem) является непрактичным и опасным по ряду причин:

- Сложность и состояние: UART — это устройство, работающее с состоянием. Необходимо постоянно проверять флаги в

LSR, корректно переключать битDLABдля настройки скорости, управлять буферами. Эта логика сложна и чревата ошибками. - Конкурентный доступ (Race Conditions): Если две программы одновременно попытаются настроить скорость или отправить данные, это приведет к хаосу и повреждению данных.

- Неэффективность: Без использования прерываний и DMA, пользовательская программа была бы вынуждена работать в режиме опроса (polling), постоянно в цикле проверяя регистр

LSR, что является крайне расточительным использованием ресурсов процессора. - Абстракция и переносимость: Адреса и некоторые особенности регистров могут незначительно меняться между версиями SoC.

Роль драйвера ядра Linux — взять на себя всю эту сложность. Когда ваша Python-программа открывает файл /dev/ttyS1 и настраивает его:

- Драйвер выполняет все необходимые операции с регистрами

LCR,DLL,DLH, чтобы установить нужный формат и скорость. - Когда вы отправляете данные, драйвер помещает их в TX FIFO и использует DMA для эффективной передачи.

- Драйвер регистрирует обработчик прерывания (ISR). Когда приходит прерывание от UART (например, "принят новый байт"), именно код драйвера выполняется, считывает данные из

RBR, помещает их в системный буфер и затем "будит" вашу программу, ожидающую чтения.

Таким образом, ядро Linux предоставляет чистый, безопасный и стандартизированный файловый интерфейс, скрывая за ним всю сложную и опасную работу по прямому управлению аппаратными регистрами UART.